Frederic T. Chong Christoforos Kozyrakis Mark Oskin (Eds.)

# Intelligent Memory Systems

Second International Workshop, IMS 2000 Cambridge, MA, USA, November 2000 Revised Papers

Lecture Notes in Computer Science Edited by G. Goos, J. Hartmanis and J. van Leeuwen

## Springer Berlin

Bertin Heidelberg New York Barcelona Hong Kong London Milan Paris Singapore Tokyo Frederic T. Chong Christoforos Kozyrakis Mark Oskin (Eds.)

## Intelligent Memory Systems

Second International Workshop, IMS 2000 Cambridge, MA, USA, November 12, 2000 Revised Papers

Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editors

Frederic T. Chong Mark Oskin University of California Dept. of Computer Science Davis, 95616 CA, USA E-mail:{chong,mhoskin}@cs.ucdavis.edu

Christoforos Kozyrakis University of California EECS Computer Science Division 415 Soda Hall 1776 Berkeley, 94720-1776 CA, USA E-mail:kozyraki@cs.berkeley.edu

Cataloging-in-Publication Data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Cognitive technology: instruments of mind : 4th international conference ;proceedings / CT 2001, Warwick, UK, August 6 - 9, 2001. Meurig Beynon ... (ed.). - Berlin ; Heidelberg ; New York ; Barcelona ; Hong Kong ; London ; Milan ; Paris ; Singapore ; Tokyo : Springer, 2001 (Lecture notes in computer science ; Vol. 2117 : Lecture notes in artificial intelligence) ISBN 3-540-42406-7

CR Subject Classification (1998): B.3, B, C, D.4, F.3

ISSN 0302-9743 ISBN 3-540-42328-1 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2001 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Steingräber Satztechnik GmbH, HeidelbergPrinted on acid-free paperSPIN 1083954006/31425 4 3 2 1 0

## Preface

We are pleased to present this collection of papers from the Second Workshop on Intelligent Memory Systems.

Increasing die densities and inter-chip communication costs continue to fuel interest in intelligent memory systems. Since the First Workshop on Mixing Logic and DRAM in 1997, technologies and systems for computation in memory have developed quickly. The focus of this workshop was to bring together researchers from academia and industry to discuss recent progress and future goals.

The program committee selected 8 papers and 6 poster session abstracts from 29 submissions for inclusion in the workshop. Four to five members of the program committee reviewed each submission and their reviews were used to numerically rank them and guide the selection process. We believe that the resulting program is of the highest quality and interest possible. The selected papers cover a wide range of research topics such as circuit technology, processor and memory system architecture, compilers, operating systems, and applications. They also present a mix of mature projects, work in progress, and new research ideas.

The workshop also included two invited talks. Dr. Subramanian Iyer (IBM Microelectronics) provided an overview of embedded memory technology and its potential. Dr. Mark Snir (IBM Research) presented the Blue Gene, an aggressive supercomputer system based on intelligent memory technology.

Several people contributed to making this workshop happen. We would like to thank the members of the program committee for the considerable time they spent during the review and selection process. David Patterson (UC Berkeley) and Mark Horowitz (Stanford), the steering committee members, provided valuable advice on the scope and the organization of the workshop. We would also like to thank Larry Rudolph (MIT), James Hoe (CMU), and the rest of the ASPLOS-IX organizing committee for their help with local arrangements, registration, financing, and the proceedings. Finally, we would like to thank all the authors that submitted their papers to this workshop.

May 2001

Fred Chong, Christoforos Kozyrakis, and Mark Oskin

## **Workshop Committee**

## **Co-chairs**

Frederic Chong Christoforos Kozyrakis (University of California at Davis) (University of California at Berkeley)

## **Steering Committee**

David Patterson Mark Horowitz (University of California at Berkeley) (Stanford University)

## **Publicity and Publications**

Mark Oskin

(University of California at Davis)

## **Program Committee**

| Krste Asanovic         | (Massachusetts Institute of Technology)      |

|------------------------|----------------------------------------------|

| John Carter            | (University of Utah)                         |

| Frederic Chong         | (University of California at Davis)          |

| Nikil Dutt             | (University of California at Irvine)         |

| Jose Fortes            | (Purdue University)                          |

| John Granacki          | (USC Information Sciences Institute)         |

| Patrick Hanrahan       | (Stanford University)                        |

| Peter Kogge            | (Notre Dame University)                      |

| Christoforos Kozyrakis | (University of California at Berkeley)       |

| Konrad Lai             | (Intel)                                      |

| Kazuaki Murakami       | (Kyushu University)                          |

| Josep Torrellas        | (University of Illinois at Urbana-Champaign) |

| Woodward Yang          | (Harvard University)                         |

|                        |                                              |

## **Table of Contents**

## **Memory Technology**

## **Processor and Memory Architecture**

## **Applications and Operating Systems**

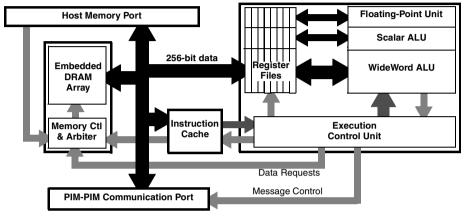

| The Characterization of Date Intensive Memory Workloads                          |     |

|----------------------------------------------------------------------------------|-----|

| on Distributed PIM Systems                                                       | 85  |

| Richard C. Murphy, Peter M. Kogge, and Arun Rodrigues (University of Notre Dame) |     |

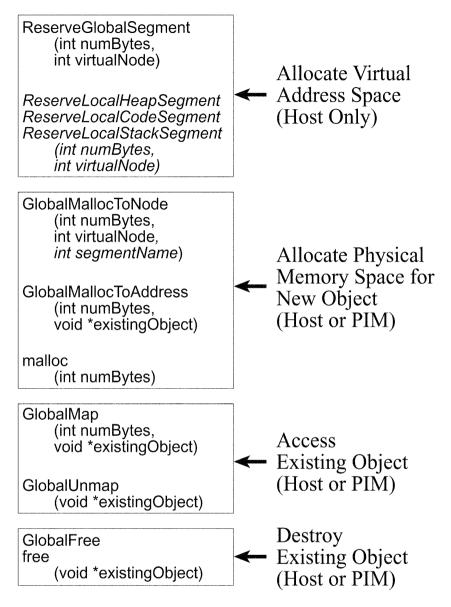

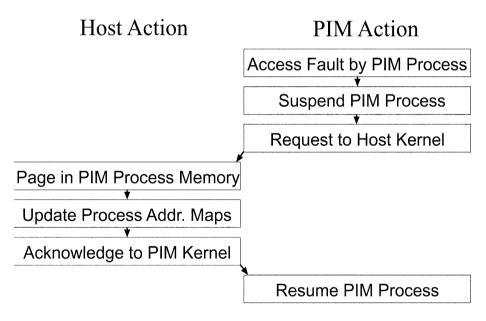

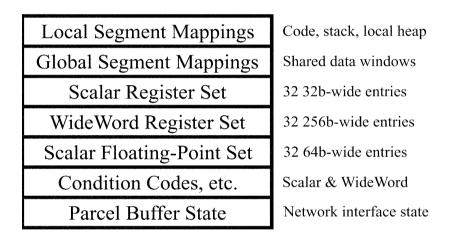

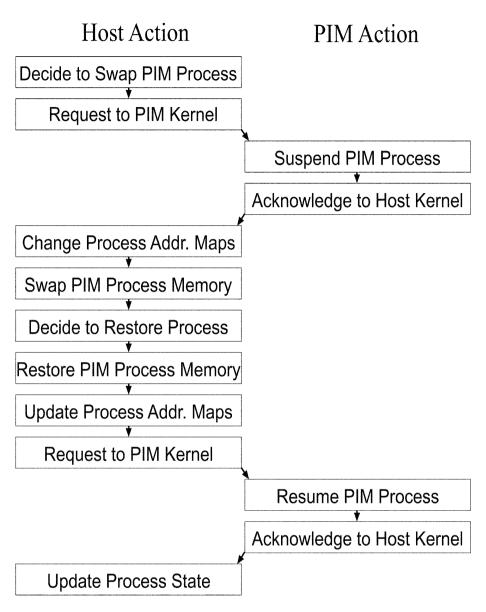

| Memory Management in a PIM-Based Architecture                                    | 104 |

Mary Hall and Craig Steele (USC Information Sciences Institute)

## **Compiler Technology**

## **Poster Session**

| Aggressive Memory-Aware Compilation                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

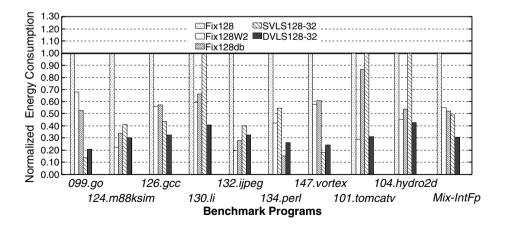

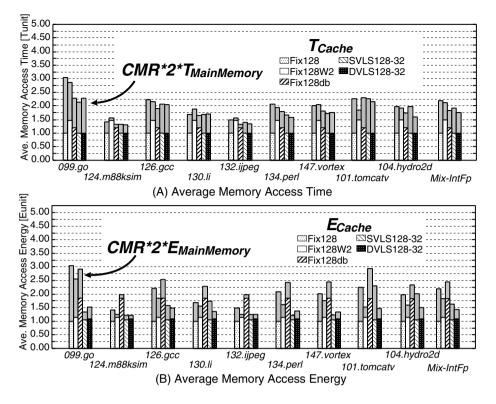

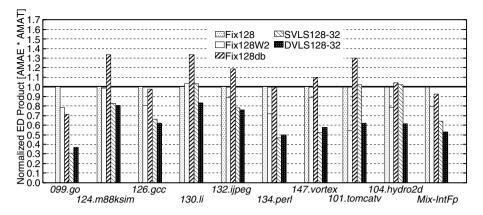

| Energy/Performance Design of Memory Hierarchies<br>for Processor-in-Memory Chips                                                                |

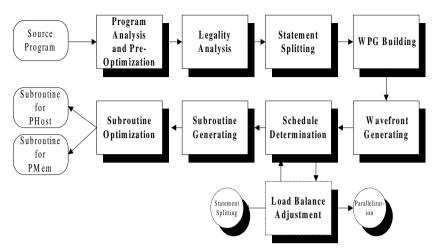

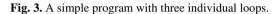

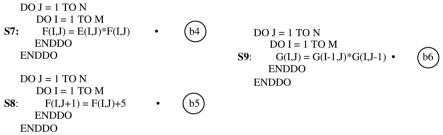

| SAGE: A New Analysis and Optimization System for FlexRAM Architecture 160<br>Tsung-Chuan Huang and Slo-Li Chu (National Sun Yat-sen University) |

| Performance/Energy Efficiency of Variable Line-Size Caches<br>for Intelligent Memory Systems                                                    |

| The DIVA Emulator: Accelerating Architecture Studies for PIM-Based Systems 179<br>Jeff LaCoss (USC Information Sciences Institute)              |

| Compiler-Directed Cache Line Size Adaptivity                                                                                                    |

| Workshop Notes                                                                                                                                  |

| Author Index                                                                                                                                    |

## A 64Mbit Mesochronous Hybrid Wave Pipelined Multibank DRAM Macro

Junji Ogawa<sup>1</sup> and Mark Horowitz<sup>2</sup>

<sup>1</sup> Fujitsu Laboratories of America jogawa@fla.fujitsu.com

<sup>2</sup> Computer Systems Laboratory, Stanford University

**Abstract.** This paper describes a high bandwidth and low latency hybrid wavepipelined data bus scheme for multi-bank DRAM macros on single chip multiprocessors. Long data bus lines inserted with multiple wave-pipelined stages at each bank input/output are further divided by periodically inserted synchronizing registers to overcome cycle time degradations due to skew and jitter effects in the wave-pipe. Each memory macro controller controls the access sequence not only to avoid internal bank access conflicts, but also to communicate with the other controllers through the hybrid bus. A SPICE simulation result is shown assuming for a 64Mbit macro comparing four 128bit wide data bus schemes. The hybrid scheme can realize over 1GHz on-die data bus for multi-bank DRAM.

## 1. Introduction

Designers have long known that the growing gap between DRAM performance and processor performance would limit system performance. With the continued scaling of process technologies, the large available silicon die area allows for the integration of DRAM and logic onto a single die. This increases the DRAM bandwidth and decreases the latency [2][3]. But with the possibility of putting multiple processors on a single die, the pressure on the DRAM bandwidth further increases [1][9][10].

Multi-banking the DRAM [14] can help ease this pressure by allowing multiple nonconflicting requests to access the DRAM concurrently [5][6]. However, even with multibanked embedded DRAM, the connection between the processing elements and DRAM macros can still be a bottleneck. This paper proposes a repeated, wave-pipelined data bus [7][8] for multi-banked DRAM macros. The proposed data bus scheme breaks the long bus lines into multiple repeated stages with a synchronizer in the middle, thus making the bus delay linear with length. We can have multiple requests or replies in flight on the line at the same time by wave-pipelining the bus. Using wave pipelining we avoid the additional delay from synchronizing register elements [4]. Jitter on the clocking line and process variation ultimately limits the length of the bus, but inserting a synchronizer in the middle alleviates this problem at the cost of some additional delay. The periodic insertion of registers represents a hybrid between a fully synchronous bus and a fully wave-pipelined bus. The proposed hybrid wave pipeline method using multiple banks can meet the high bandwidth requirement in future SOCs and multiprocessors.

## 2. Concept of the Hybrid Wave Pipeline

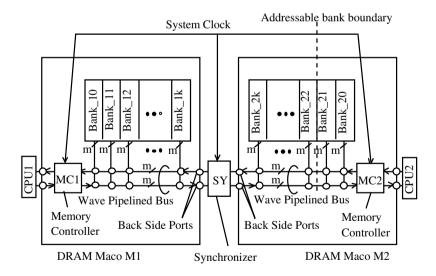

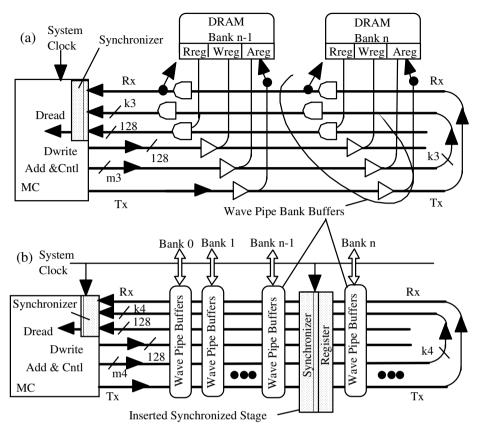

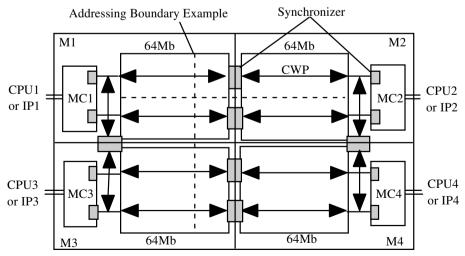

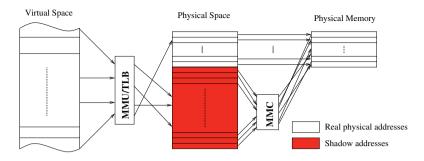

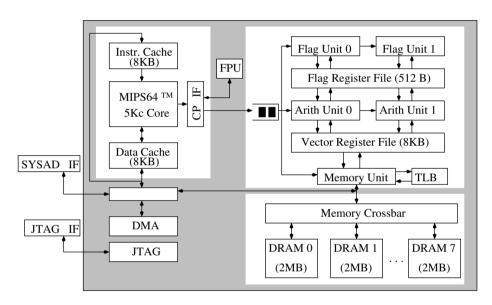

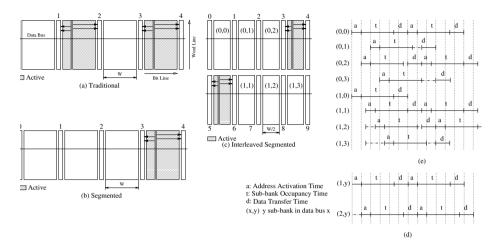

Figure 1 shows the concept of the DRAM data path hybrid pipeline scheme. Two macros are shown in figure 1, and each macro is composed of a memory controller (MC) and a DRAM macro, which consists of k independent banks, each with *m*-bit wide data input/output ports. Figure 1 shows how multiple DRAM macros can be shared between different processors or memories. Two multi-bank DRAMs are connected together using their backside ports. Each macro has two dedicated clock wave pipeline data paths inside, and pipe expansion is enabled through the backside connection using synchronizers to share the macros between different requestors such as a CPU or other IP macro. A system clock needs to be provided only into each memory controller and into the mesochronous synchronizers. Each of the two requestors can access all banks up to the *addressable bank boundary*. The addressable bank boundary is set up statically before memory access operations begin. One of the two requestors can access memory banks beyond the physical boundary between macros through the synchronizer.

The purpose of hybrid wave pipelining is to balance high bandwidth and low latency cost-efficiently on the data path between the memory controller and memory banks. For future multiprocessor systems having multiple access requestors to a memory macro, the wide I/O port giving high bandwidth without loss of latency is a desirable feature of the on-die macro.

Assuming multi-banking is implemented, there are many ways to achieve a high bandwidth. For example, an easy way is simply to give a wide port to each bank and making the whole memory macro I/O wider. However, getting higher bandwidth in this manner is costly in terms of the physical wiring area. Moreover, the bandwidth is available only to CPUs and IP macros designed to handle it, for example, a special

**Fig. 1.** Concept of Hybrid Pipeline Scheme; Each of two DRAM macros, M1 or M2, has *k* banks and a memory controller (MC). Outgoing and incoming data between MC and banks travel on the wave-pipelined bus. The opposite end of the wave-pipelined bus connects to a synchronizing register clocked by a system clock.

purpose streaming-data machine [1][9][12][18]. Another way to achieve high bandwidth is to use a mainstream high-speed I/O technique in the standard DRAM such as RAMBUS [3][13][16], DDR or SLDRAM [17], and for the embedded macro data paths as well. However, these techniques are optimized for board-level data buses where wiring is extremely tight, and moreover, they would require an expensive PLL in each RAM bank if they were implemented on-chip.

It is easier to increase wires and banks on-chip than on a PC board, but there are still trade-offs required to harmonize latency and bandwidth, while recognizing that wires are not free [13]. The proposed hybrid wave pipeline scheme is a candidate solution that maximizes the bandwidth per wire while maintaining short latency and reducing the cost of communication paths between different access requestors in future large VLSI chips.

Before describing the hybrid wave pipeline scheme in detail, in the next section we analyze the latency and area trade-offs for different bank sizes and IO widths.

#### 3. Analysis of Latency and Cost of Multi-banked DRAM

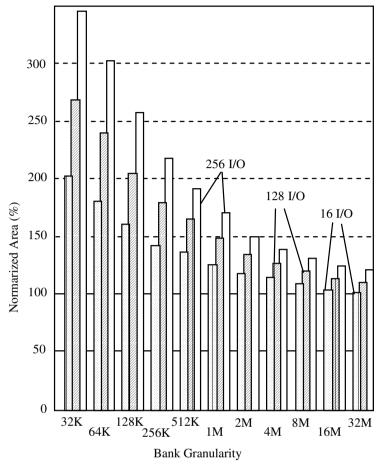

One of the crucial parameters in designing multi-banked DRAM macros is the bank size. While using smaller banks to get high bandwidth decreases the bank access time and usually the macro access time, the area overhead increases. Assuming layout using a 0.18um embedded DRAM cell technology and 256Mbit total on die memory, Figures 2 and 3 show estimated area and latency versus bank granularity. The base design is for a macro composed of 8 x 32Mbit banks using a 16bit port. Figure 2 shows the normalized area of a 256Mbit DRAM macro for a variety of bank sizes using 16bit, 128bit or 256bit access port each. The figure shows that the area increases sharply as the bank granularity is decreased to get high bandwidth, especially for the wide I/O banks.

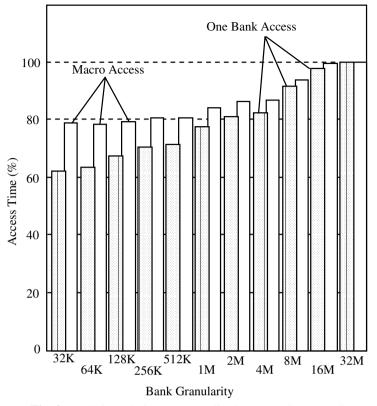

Figure 3 plots the bank and macro access time tRAC against the bank size. For the bank sizes shown, both the bank and macro access times improve with decreasing bank size mainly due to shorter word and/or bit lines. A smaller bank granularity and a wider bus achieve higher bandwidth, and one can also reduce the random access latency, tRAC, by 20% compared to the base design by tripling the macro size with 128 or more I/O ports. However, from the cost-performance point of view, 1Mbit or 2Mbit bank size with 128-bit or 256-bit in a 0.18um cell technology are good alternatives, balancing the bandwidth and latency while paying a much lower (~1.5X) area penalty.

Using at 0.18um DRAM cell technology, approximately 256Mbit of DRAM can be implemented on a single die. Based on the above estimation, it is a good choice to divide the memory on die into 128 x 2Mbit banks with a 128-bit width. There's still flexibility in selecting the number of macros to divide the 256Mbit memory into, corresponding to the number of access requestors on die, each of which needs an independent controller.

### 4. Data Bus Design Options

#### 4-1. Fully Synchronous and Asynchronous Bus

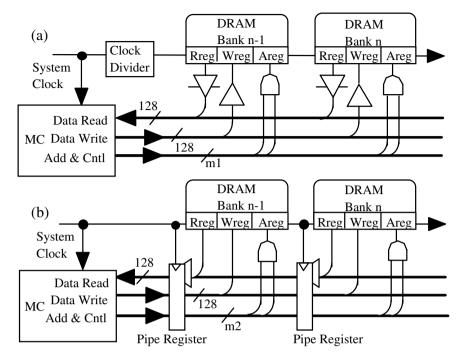

Figure 4(a) shows a conventional data bus (CBUS) connecting all of the banks using dedicated read and write buses. This method has been widely used for a long time in actual standard DRAM designs due to the area savings by sharing wires physically for the bus line with all of the banks. As technology scales, sharing the bus wires with banks in a

**Fig. 2.** Bank Granularity vs. Estimated Macro Area (normalized.) The base design is a 256 Mbit DRAM divided into 8 banks with a 16-bit wide ports. The three kinds of bars indicate 16-bit wide, 128-bit wide and 256-bit wide port macro respectively.

large part of the chip makes it difficult to keep up with high data rate required from DRAM. This scheme needs thicker upper layer metal wires for the bus to reduce resistance, and also spacing between bus wires must be relaxed to reduce capacitance and crosstalk noise. The end result is serious area cost and performance degradation for future large chips.

Figure 4(b) shows a fully synchronous pipeline scheme (FSP) [4], also using dedicated read and write buses. In this scheme, both buses are pipelined using registers at each bank I/O. The FSP scheme has the advantage of higher bandwidth than the conventional scheme, however the latency of the FSP bus is larger and increases with pipe depth, since each data token is advanced only one segment per clock cycle. Another advantage of FSP is the ease of increasing its maximum frequency as long as the system clock is distributed with small skew. Finally, the FSP scheme can use finer metal pitch (lower layer metals) than the conventional bus scheme because the paths between registers, corresponding to the pipe stages, are smaller.

Fig. 3. Bank Granularity vs. Normalized Access Time (tRAC)

Another choice is a fully asynchronous bus. In general, a fully asynchronous bus can't achieve higher bandwidth nor can it achieve lower latency in real designs due to the time overhead for the inevitable handshaking between stages. On the other hand, a wavepipeline method with mesochronous synchronization has been proposed as a possible solution to achieve bandwidth close to the fully synchronous scheme and latency close to the conventional scheme [7][8]. However, wave-pipelining design is difficult due to the critical skew and jitter control problem, and the difficulty increases as the design scales up. A longer depth wave-pipeline increases skew due to dynamic voltage and temperature variation and on-chip process variation.

#### 4-2. Hybrid Scheme Based on Dedicated Clock Wave-Pipeline

To overcome the problems discussed in the previous section, we propose a hybrid pipeline scheme (HBP) based on a dedicated clock wave-pipelined bus (CWP), in which wave-pipeline segments are connected together periodically with synchronizers.

Figure 5(a) shows the concept of the CWP scheme. Each bus is divided into multiple segments, each of which corresponds to one bank I/O. Instead of using registers in every stage as in the FSP scheme, we wave-pipeline the bus using combinational logic blocks at each bank to buffer the data. Tx and Rx denote clocking signals. Tx is a dedicated clock used for the write bus, and Rx is a dedicated clock for the read bus. Rx and Tx can be generated independently, as long as they have the same frequency. As seen in figure 5(a),

Fig. 4. (a) Conventional Bus (CBUS), (b) Fully Synchronous Pipeline Bus (FSP)

if the macro is not connected to another macro through a synchronizer, it is possible for the Rx signal to be generated by the return path of the Tx signal at the end of the wave pipe opposite the memory controller.

Both clocking signals propagate along replica delay lines, which match the delay of the data lines. The memory controller includes a mesochronous synchronizer to receive read data associated with Rx and then synchronize the data to the system clock domain. The clocking signals Tx and Rx facilitate proper latch timing at the inputs and outputs of the DRAM banks. The mismatch between Tx and Rx at any memory bank doesn't cause a problem provided the memory controller is programmed to insert appropriate null data cycles when sending read/write requests so that the actual write and read latch timings at the bank I/O are spaced by greater than the minimum bank cycle time. In a given cycle, only the timing relationship between Tx and write data or between Rx and read data needs to be controlled.

Figure 5(b) shows the hybrid pipeline scheme, HBP. In the HBP scheme, a set of synchronizers and registers are inserted between two buses, each of which has multiple wave-pipeline stages. Synchronization adds at most one additional system clock cycle to the data between wave-pipeline stages. In the HBP scheme, the load of the system clock can be greatly reduced compared to the FSP scheme. The maximum numbers of wave-pipe stages is determined roughly by limiting the maximum skew generated in the pipeline to less than ½ of the clock period.

Fig. 5. (a) Dedicated Clock Wave Pipeline Bus, (b) Hybrid Scheme

### 4-3. Hybrid Circuit and Stage Operation

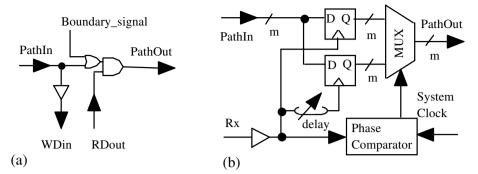

Figure 6(a) shows the unit circuit of the wave-pipeline. An or-and (OA) gate receives both traveling data from the previous neighbor stage, *PathIn*, and outgoing data from the bank, *Rdout*, and generates the next stage in the wave-pipeline, *PathOut*. The write input of the bank, *Wdin*, is buffered from *PathIn*. The static signal *Boundary\_signal* is used to shut off the pipeline at an addressable memory boundary. The wave-pipeline stage has negligible area penalty compared to a CBUS, due to its use of the simple OA repeater component. Assuming the same wire pitch used for the bus line, the area penalty of the CWP bus compared to the CBUS is less than 10%. The total macro area penalty is less than 0.6%, assuming the bus occupies 6% of the memory macro. Usually, a CBUS wire is wider than a CWP bus wire, so the area penalty will be reduced in an actual design.

To latch write-in data and addresses correctly into a RAM bank, each uses its local Tx clock, which can also be used to activate the bank. On the other hand, the MC needs a mesochronous controller to receive its 128-bit data correctly. The internal MC synchronizer needs an initializing operation to learn the pipe delay characteristics. Individual banks don't need synchronizers, even while sending read-out data after bank activations triggered by Tx, because the MC knows when the write or read enable signal should be sent, and how many null data cycle should be inserted to skip a cycle.

Fig. 6. Hybrid scheme Unit Circuit: (a) CWP bank write data-in buffer and OA, (b) Synchronizer

Figure 6(b) shows a simple embodiment of a mesochronous synchronizer, which has 2 flip-flops for 2-way interleaving and a multiplexor or 2x2 switch for every data line, and one shared phase comparator and adjustable delay element. If the frequency is high, more interleaving flip-flops are needed with finer gradations of clock phase. Dynamic phase adjustment and an accurate phase-interpolator should be provided in the synchronizer for fine-tuning. Although synchronizers both in the MC and in the middle of the wave-pipe cost additional layout area, the penalty is less than 1% of the macro area due to the relatively small number needed in the HBP scheme.

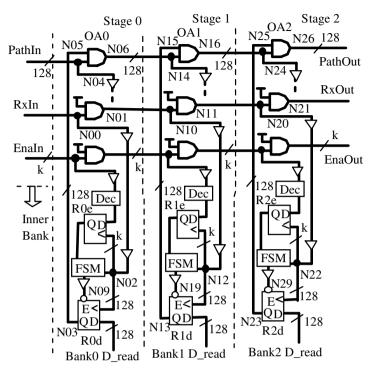

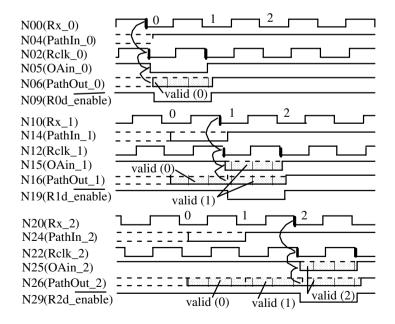

Figure 7 shows the CWP read path circuit and the bank read data registers in detail. A timing diagram of read operation in Figure 7 is shown in Figure 8. Before starting the operation, all lines are pre-charged to "1" and transition only when sending a "0". The dedicated reference clock, Rx, always travels on the replica wires in the same direction as outgoing data at the same time, as shown in the figure, so that data and clock (Rx) propagation delay between Pathin (N04)-N06-N14 and RxIn (N00)-N01-N10 are matched to minimize skew.

R0d, R1d and R2d denote 128-bit wide read data registers in three banks 0, 1, and 2, respectively. The registers are clocked by their local Rx signals (N02, N12 and N22). Outputs data N03 from R0d goes to N05, which is one of two inputs of the wave-pipe OA gate (the OR gate for the Boundary-signal is not shown in the figure for simplicity). Clock in to data out delay between RxIn (N00)-N02-N03-N05-N06 and N01-N10-N12-N13-N15-N16 should be matched as well. In this way, the maximum frequency of the read operation is limited mainly by the sum of flip-flop delay (Tsetup + Tck-q) plus data and clock skew, as long as the inserted synchronizer can follow the frequency.

Since high bandwidth requires a large number of wires in the wave pipeline, reducing the area of the bus is an important issue in an actual design. We can wire the bus using the intermediate metal layers for data lines, which typically have twice the resistance of the top metal layers. Since over half of the delay is contributed by skew and flip-flop related timing such as clock to Q delay at maximum bandwidth, the delay contributed by wires is not dominant in the hybrid scheme. Therefore, it is possible to reduce the area penalty of the bus by using the intermediate metal layers without significantly increasing latency. The resultant macro overhead of this HBP scheme is estimated to be around 2%.

Fig. 7. Wave Pipeline Circuit for Data Read in HBP and CWP

Fig. 8. Timing Diagram of the Wave Pipeline Circuit (see. Figure 7)

#### 4-4. Comparison of Bandwidth and Latency

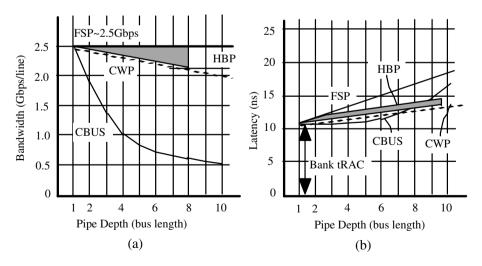

Figure 9 shows bandwidth and latency comparisons for the four bus schemes, CBUS, FSP, CWP and HBP, each with 128-bit input/output and 2Mbit banks. For the simulations, we used a 0.18um CMOS logic circuit technology with 0.18um DRAM cell technology. (We expect future processes aimed at SOC will combine high-density DRAM cells with high-speed CMOS transistors for logic.)

Figure 9(a) and 9(b) results were obtained using SPICE simulation. In our SPICE simulations, we modeled the power supply distribution using an RC mesh, and forced a dynamic voltage variation by attaching piece-wise linear noise current sources at each bank representing the bank transient current. The noise is initially adjusted to cause a 5% p-p jitter on the path in each 3-sigma worst-case process corner in order to quantify skew and performance degradation. The system clock was assumed relatively clean with only a fixed estimated skew of 120psec.

Assuming use of intermediate metal layers for the bus lines and 2Mbit bank size, the fully synchronous bus, FSP, has four times higher bandwidth than that of the CBUS when the pipeline depth is over eight, as shown in Figure 9(a). However, under the same conditions, the FSP has at least 30% higher latency than the conventional scheme, as shown in Figure 9(b). Wave pipelining in CWP can achieve both high bandwidth and low latency so that the hybrid scheme, HBP, can realize bandwidth close to FSP and latency close to CWP even with the longer length bus, as long as synchronizers are inserted periodically.

The HBP advantage will increase depending on the bus length and the degree to which future wire technologies can scale RC characteristics. In fact, the wave pipeline itself has a length limit depending on the process variation and jitter within each pipe region for a given clock frequency. This limit can be reduced by: 1) using simple OA-buffers in replicated layout for both data and dedicated clock lines as explained above, and 2) inserting a synchronizer in the middle of the path.

Fig. 9. (a) Bandwidth vs. Pipe Depth, (b) Latency vs. Pipe Depth

### 4-5. Taking Advantage of the Latency Difference between Banks

The MC controls access sequences [5][10][11] when conflicting bank addresses arrive. The MC design could be enhanced to manage the latency difference of each bank and pass the data to the requester when it is ready. However, to take advantage of the lower latency to nearby banks, a handshake is required between the access requestor and the memory macro to know when the response from the memory returns. Advanced multiprocessors, including stream specific machines, generally use deep-pipe processing, and it seems to be rather difficult to take advantage of these kinds of address dependent latency differences without stalling their pipelines frequently, especially when the difference in total latency from different banks is small. In future large chips, if the area ratio between the processing units and the DRAM becomes smaller and the ratio  $\Box$ tRAC/tRAC becomes larger, it will become more desirable to take advantage of the latency difference.

## 5. Embedded Macro Architecture

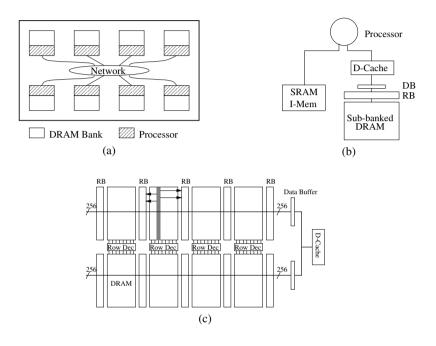

## 5-1. 64Mbit Macro Architecture

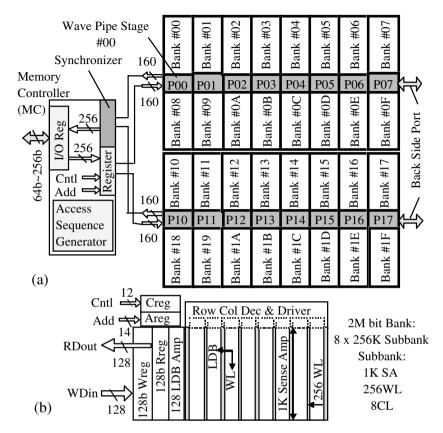

Figure 10(a) shows the block diagram of a 64Mbit macro; four 64Mbit macros are on a die. This 64Mbit macro has 32 x 2Mbit banks and two streams of wave pipe paths. Figure 10(b) shows the 2Mbit bank in detail, which is divided into 8 blocks having 1K sense-amplifier, 256 word lines, 128-bit read and write data buffers, address registers, and control register and logic.

In Figure 10(a), two streams of wave pipeline path, p00 to p07 and p10 to p17, are shown. Each pij denotes one pipe stage data path circuit block shared between two banks. For example, the stage p00 is used for both bank #00 and bank #08. An internal memory controller manages access sequence control not only to arbitrate access requests from different source [5], but also to manage the wave pipelining to prevent bank-to-bank access conflicts. The macro can have two ports, a main port on the front side near the MC, and a sub-port on the backside at the far end of the wave pipeline. In the HBP scheme, the backside port connects to the synchronizer (not shown in Figure 10.)

In terms of the simultaneous access to one macro from multiple requestors, the number of accessible ports is equal to the number of wave-pipeline streams designed into the macro.

### 5-2. Four-Tile Configuration on a Single Chip

Figure 11 shows a configuration example of four 64Mbit macros, M1-M4, using a hybrid pipeline with synchronizers connecting M1 to M2 and M3 to M4. If each memory controller has additional logic, M1 can connect to M3, and M2 can connect to M4 vertically on the left and right sides in this figure.

By connecting two banks at their backsides as shown in Figure 1 and 11, and inserting the synchronizer, the wave pipeline becomes expandable. As the path length increases, which means a deep pipe, this hybrid scheme gains an advantage compared to both FSP and CWP. The wave pipeline itself has a length limit depending on the process variation and jitter within each pipe region, but inserting a synchronizer reduces this limit.

Fig. 10. Block Diagram of a 64Mbit DRAM Macro. (a) 64Mbit Macro, (b) 2Mbit Bank

Fig. 11. Example Block Diagram of Four-Tile Configuration

## 6. Conclusion

Future systems will demand higher bandwidth and lower latency from DRAM. Moving to embedded DRAM improves both of these metrics, but the on-chip bus to the DRAM can still be a bottleneck. We have proposed a hybrid bus scheme employing wave-pipelining and periodic synchronization to achieve a bandwidth near that of a fully synchronous bus and latency near that of a conventional bus.

## 7. Acknowledgements

The author thanks Dr. Ken Mai and Dr. Ron Ho of Stanford Computer Systems Laboratory, Dr. Yasuo Hidaka of HAL Computer Systems Inc., and Mr. William Walker of Fujitsu Laboratories of America for useful discussions, comments and encouragement.

## References

- [1] [MaiISCA'00] Ken Mai, et al., "Smart Memories: A Modular Re-configurable Architecture," In proceedings of the 7<sup>th</sup> Annual International Symposium on Computer Architecture, pages 161-171, June 2000.

- [2] [PattersonMicro'97] David Patterson, et al., "A Case for Intelligent RAM," *IEEE Micro*, pages 34-44, Mar./Apr. 1997.

- [3] [CrispMicro'97] Richard Crisp, "Direct RAMBUS Technology," *IEEE Micro*, pages 18-28, Nov./Dec 1997.

- [4] [TakahashiISSCC'00] O. Takahashi, et al., "1GHz Fully-Pipelined 3.7ns Address Access Time 8kx1024 Embedded DRAM Macro," *In Digest of Technical Papers ISSCC 2000*, Pages 396-397, Feb. 2000.

- [5] [WatanabeISSCC'99] T. Watanabe, et al., "Access Optimizer to overcome the 'Future Walls of Embedded DRAMs' in the Era of Systems on Silicon," *In Digest of Technical Papers ISSCC 1999*, Pages 370-371, Feb. 1999.

- [6] [KimuraISSCC<sup>99</sup>] T. Kimura, et al., "64Mbit 6.8ns Random Row Access DRAM Macro for ASICs," *In Digest of Technical Papers ISSCC 1999*, pages 416-417, Feb. 1999.

- [7] [YoonJSSC'99] Hongil Yoon, et al., "A 2.5-V, 333-Mb/s/pin, 1Gbit, Double-Data-Rate Synchronous DRAM," *IEEE Journal of Solid-State Circuits*, Vol.34 No11, pages 1589-1597, Nov. 1999.

- [8] [ManVLSI'96] Jin-Man Han, et al., "Skew Minimization Techniques for 256-Mbit Synchronous DRAM and Beyond," 1996 Symposium on VLSI Circuits Digest of Technical Papers, pages 192-193, June 1996.

- [9] [OluktonISCA'99] K. Olukton, et al., "Improving the performance of speculative Parallel Applications on the Hydra CMP," *In proceedings of the 1999 ACM International Conference* on Supercomputing, June 1999.

- [10] [RixnerISCA'00] Scott Rixner, et al., "Memory Access Scheduling," In proceeding of the 7<sup>th</sup> Annual International Symposium on Computer Architecture, pages 128-138, June 2000.

- [11] [Panda'99] Preeti R. Panda, N. D. Dutt, A. Nicolau, "Memory Issues in Embedded System-On-Chip –Optimization and Exploration-," Kluwer Academic Publishers, ISBN 0-7893-8362-1, 1999.

- [12] [RixnerISM'98] Scott Rixner, et al., "A Bandwidth Efficient Architecture for Media Processing," In Proceedings of the 31st Annual International Symposium on Microarchitecture, pages 3-13, Nov.-Dec. 1998.

- [13] [RAMBUS-website] http://www.rambus.com/developer/quickfind\_documents.html

- [14] [Mosys-data sheet] http://www.mosysinc.com/prelease3/, MC80364K64, 64Kx64 PBSRAM.

- [15] [HorowitzSRC'99] Mark Horowitz, et al., "The Future of Wires," SRC White Paper: Interconnect Technology Beyond the Roadmap, 1999, (<u>http://www.src.org/cgi-bin/deliver.cgi/sarawp.pdf?</u>/areas/nis/sarawp.pdf).

- [16] [MukaiISSCC'00] Hideo. Mukai, et al., "New Architecture for Cost-Efficient High-Performance Multiple-Bank," In Digest of Technical Papers ISSCC 2000, Pages 400-401, Feb. 2000.

- [17] [ParisISSCC'99] Lluis. Paris, et al., "A 800MB/s 72Mb SLDRAM with digitally-Calibrated DLL," In Digest of Technical Papers ISSCC 1999, Pages 414-415, Feb. 1999.

- [18] [GealowJSSC'99] Jeffrey C. Gealow, et al., "A Pixel Parallel Image Processor Using Logic Pitch-Matched to Dynamic Memory," *IEEE Journal of Solid-State Circuits*, Vol.34 No6, pages 831-839, Nov. 1999.

## Software Controlled Reconfigurable On-chip Memory for High Performance Computing

Hiroshi Nakamura<sup>1</sup>, Masaaki Kondo<sup>1</sup>, and Taisuke Boku<sup>2</sup>

Research Center for Advanced Science and Technology, The University of Tokyo 4-6-1 Komaba, Meguro-ku, Tokyo, 153-8904, Japan {nakamura,kondo}@hal.rcast.u-tokyo.ac.jp

Institute of Information Sciences and Electronics, University of Tsukuba 1-1-1 Tennodai, Tsukuba-shi, Ibaraki, 305-8573, Japan taisuke@is.tsukuba.ac.jp

Abstract. The performance gap between processor and memory is very serious problem in high performance computing because effective performance is limited by memory ability. In order to overcome this problem, we propose a new VLSI architecture called SCIMA which integrates software controllable memory into a processor chip in addition to ordinary data cache. Most of data access is regular in high performance computing. Software controllable memory is better at making good use of the regularity than conventional cache.

This paper presents its architecture and performance evaluation. In SCIMA, the ratio of software controllable memory and cache can be dynamically changed. Due to this feature, SCIMA is upper compatible with conventional memory architecture. Performance is evaluated by using CG and FT kernels of NPB Benchmark and a real application of QCD (Quantum ChromoDynamics). The evaluation results reveal that SCIMA is superior to conventional cache-based architecture. It is also revealed that the superiority of SCIMA increases when access latency of off-chip memory increases or its relative throughput gets lower.

## 1 Introduction

Processor performance has been improved drastically by clock acceleration and ILP (instruction-level parallelism) extraction techniques. Main memory performance, however, has not been improved so much. This performance disparity called memory wall problem[1] is very serious. To solve this problem, cache memory is widely used. However, cache is not effective in large scientific/engineering applications[2] because data set is much larger than cache capacity. In high performance computing (abbreviated as HPC hereafter) area, although future advancement of semiconductor technology will certainly enlarge on-chip cache size, the whole data set can never reside in data cache because the data size itself grows in proportion to processing ability.

The ability of memory system is characterized by two factors, latency and throughput. There have been proposed a lot of latency hiding techniques, such as larger cache line, prefetching, lock-up free cache, and so on. However, all of these latency hiding techniques lead to increase of the pressure on memory bandwidth. Because the bandwidth of off-chip memory will not grow as rapid as processor performance, reducing off-chip memory traffic is essentially required.

Therefore, it is important firstly to exploit temporal locality and making good use of wide on-chip cache bandwidth. Secondly, decreasing the number of off-chip memory accesses is helpful for reducing performance degradation caused by long memory access latency.

As for the first issue of exploiting temporal locality, cache blocking [3] is a well-known and promising optimization. Unwilling line conflicts, however, still increase memory traffic and degrade performance. To solve this problem, good tile size selection algorithm [4] and padding technique [5] have been proposed so far. However, programs should be rewritten carefully depending on the detail of both the cache structure and the data array structure. Moreover, these techniques cannot completely remove line conflicts among different data arrays. For example, they cannot avoid the unfortunate but frequent situations where data with little reusability pollutes data cache and flushes out other data which will be used soon.

As for the second issue, the number of off-chip memory accesses can be decreased by making the size of each data transfer large. Adopting larger cache line could be one solution. However, unnecessary data transfer must be avoided because it wastes memory bandwidth which is the most valuable resource. Thus, for non-consecutive data access, this solution is harmful.

The essential reason for these problems is that it is by far difficult for hardware to control data location and data replacement. Because most of the data accesses in HPC (High Performance Computing) applications are regular, it is reasonable to control data location and replacement by software. Thus, we propose a new VLSI architecture named *SCIMA: Software Controlled Integrated Memory Architecture.* SCIMA integrates software-controllable addressable memory into processor chip as a part of main memory in addition to ordinary cache. Hereafter, we call that memory "On-Chip Memory" (As opposed to that, we call off-chip main memory "Off-Chip Memory").

Since On-Chip Memory is explicitly addressed by software, only the required data is transferred into the On-Chip Memory without flushing out other required data. Unfortunate conflicts can be avoided. In this point, On-Chip Memory is better at exploitation of temporal locality than cache. Therefore, SCIMA has the potential to solve the problems of cache and achieve higher performance.

## 2 SCIMA

#### 2.1 Overview

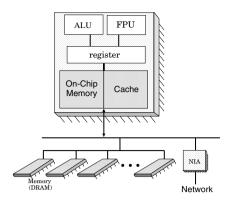

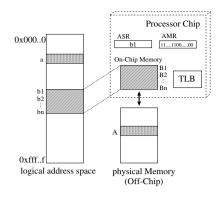

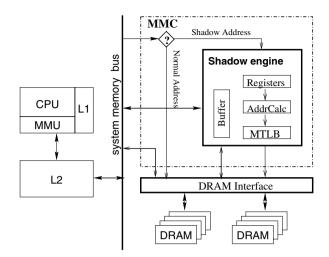

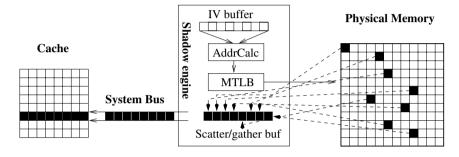

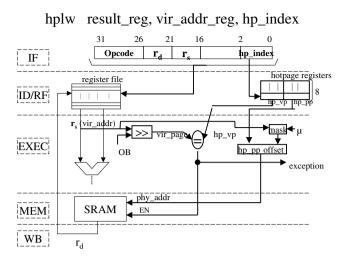

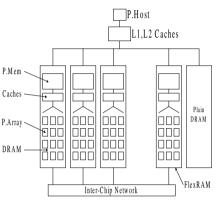

Fig. 1 shows the schematic view of the proposed architecture *SCIMA*. In SCIMA, addressable On-Chip Memory is integrated into the processor chip in addition to ordinary cache.

Location and replacement of data are controlled by software explicitly in On-Chip Memory, whereas those are controlled by hardware implicitly in cache. We

Fig. 1. Overview of SCIMA

employ SRAM as the On-Chip Memory. Since our target is HPC applications, the whole data cannot reside in On-Chip memory even if DRAM is used. Thus, we give higher priority to speed rather than capacity. Cache is still provided to work for irregular data accesses.

#### 2.2 Address Space

On-Chip Memory occupies one consecutive part of logical address space. We assume On-Chip Memory is much larger than ordinary page. Then, frequent TLB misses degrade performance seriously if On-Chip Memory is controlled by ordinary TLB. Therefore, On-Chip Memory is treated as a large page. Two special registers are introduced to identify the On-Chip Memory area as shown in Fig. 2.

- On-Chip Address Mask Register (AMR): This mask register indicates the size of On-Chip Memory. If the least significant m bits of AMR are 0, On-Chip Memory size is  $2^m$  byte.

- On-Chip Address Start Register (ASR): This register holds the beginning logical address of On-Chip Memory. This address must be aligned to the multiple of On-Chip Memory size.

The following equation tells whether the given address is within the On-Chip Memory area or not.

if (a given address & AMR) == ASR then On-Chip Memory area (1)

#### Inclusion Relation Between On-Chip Memory and Cache

All the address space has a cacheable/uncacheable property. This property is managed by TLB and page-table mechanisms like the ordinary current processors. In SCIMA, the On-Chip Memory space, which is not under the control of

Fig. 2. Address Space

TLB, is always handled as uncacheable. Therefore, there is no inclusion relation between On-Chip Memory and cache.

#### 2.3 Data Transfer Among Memory Hierarchy

The following two kinds of data transfers are available.

- register  $\leftrightarrow$  On-Chip Memory  $\leftrightarrow$  Off-Chip

- register  $\leftrightarrow$  cache  $\leftrightarrow$  Off-Chip Memory

Ordinary load/store instructions invoke transfers between registers and On-Chip Memory when the accessed address is within On-Chip Memory area. Otherwise, they access cache as usual and invoke line transfer when cache misses.

**page-load and page-store** Data transfers between On-Chip Memory and Off-Chip Memory are invoked explicitly by *page-load* or *page-store* instructions which are newly introduced. Notice that the term of *page* is different from ordinary page used in virtual memory. In this paper, *page* is a data unit transferred by one *page-load* or *page-store*. The size of page is assumed to be several KBytes. The source/destination addresses and the size of data transfer are identified by these instructions. These instructions can specify block-stride data transfer which can pack non-consecutive data of Off-Chip Memory and transfer into a consecutive area of On-Chip Memory. This is helpful for effective use of limited On-Chip Memory area and Off-Chip bandwidth.

#### 2.4 Reconfiguration of On-Chip Memory and Cache

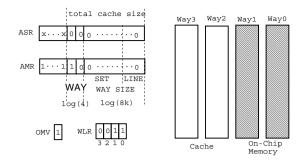

Total memory size which is available within a processor chip depends on semiconductor technology and the number of transistors devoted to the processor core. It is a difficult problem to decide the best ratio of cache and On-Chip Memory

Fig. 3. Example of On-Chip Memory and Cache Configuration

sizes under these constraints. The answer highly depends on the characteristics of target applications. Thus, we propose a reconfiguration mechanism where On-Chip Memory and cache share the hardware memory structure and the ratio of them can be changed on the same hardware. Due to this feature, SCIMA is upper compatible with conventional memory architecture. This subsection shows the hardware mechanism.

#### Hardware Mechanism

In addition to ASR and AMR described in section 2.2, we introduce the following special registers for reconfiguration of On-Chip Memory and cache.

- Way Lock Register (WLR): The bit width of this register is equal to the degree of cache associativity (the number of ways): If the bit of the corresponding way is set to on, that way is locked as On-Chip Memory.

- On-chip Memory Valid(OMV): This register has 1 bit entry which indicates whether any way is utilized as On-Chip Memory.

Fig. 3 shows an example of configurations. This figure illustrates the case where 32KB 4way cache is divided into 16KB 2way cache and 16 KB On-Chip Memory. On-Chip Memory area is assigned by a system call. When the system call is executed, data in the corresponding ways is flushed out, the corresponding bits of the WLR and OMV are set to on, and the right values are set to AMR and ASR. The WAY bits of AMR indicate the number of ways locked as On-Chip Memory and the WAY bits of ASR indicate the way from which On-Chip Memory is allocated. In Fig. 3, the WAY bits of AMR are 10 and those of ASR are 00. This indicates that two ways are utilized as On-Chip Memory and locked beginning from way 0. Table 1 shows the possible configurations of On-Chip Memory in the example of Fig.  $3^3$ .

<sup>&</sup>lt;sup>3</sup> Note that if OMV is 1, WLR is determined by the WAY bits of ASR and AMR. Otherwise, all the bits of WRL is 0. Therefore, exactly speaking, WRL is redundant information.

| On-Chip     | WAY bits | WAY bits | Ways utilized as |      |     |

|-------------|----------|----------|------------------|------|-----|

| Memory size |          |          | On-Chip Memory   | WLR  | OMV |

| 32KB        | 00       | 00       | way0,1,2,3       | 1111 | 1   |

| 16KB        | 00       | 10       | way0,1           | 0011 | 1   |

|             | 10       | 10       | way2,3           | 1100 | 1   |

| 8KB         | 00       | 11       | way0             | 0001 | 1   |

|             | 01       | 11       | way1             | 0010 | 1   |

|             | 10       | 11       | way2             | 0100 | 1   |

|             | 11       | 11       | way3             | 1000 | 1   |

| 0KB         |          | —        | N/A              | 0000 | 0   |

Table 1. Configuration of On-Chip Memory

## Actions of Memory Access

When a memory access occurs, the accessed address is checked whether it is within the On-Chip Memory area or not by using ASR and AMR (equation 1). If the access is for On-Chip Memory, the WAY part of the accessed address bits indicates the way to be accessed. In the example of Fig. 3, if the WAY part of the accessed address is 00, Way 0 is accessed. The important point is that the sets to be accessed are determined by SET bits of Fig. 3 no matter whether the address is within On-Chip Memory or not. Due to this feature, critical path does not get longer than ordinary cache access. The followings are the procedure of memory access:

- 1. The corresponding sets decided by SET bits of the address are accessed. In parallel with this access, whether the address is within On-Chip Memory area or not is decided by ASR, AMR and OMV.

- 2. If the accessed address is within On-Chip Memory, the data from the corresponding way (decided by WAY bits) is selected. Otherwise, ways whose WLR is 0 are accessed as ordinary cache.

## 2.5 Other Architectural Issues

We must consider other architectural issues. One is the guarantee of correct access order of On-Chip Memory and the other is coherence problem between cache and Off-Chip Memory. The former issue implies that execution of pageload/page-store and load/store instructions should wait for the completion of preceding those instructions if the accessed address is the same location on On-Chip Memory. The latter issue implies that if a certain Off-Chip Memory area is accessed by page-load/page-store instructions when cache holds the data of that area, consistency between cache and Off-Chip Memory must be kept. See [6] for the detail description of these issues.

## 2.6 Benefit of On-Chip Memory

The benefit of On-Chip Memory is summarized as follows.

1. better use of temporal locality

Even though temporal locality of data access is extracted, for example by tiling, unwilling line conflicts prevent cache from making good use of the locality. Especially, conflicts between data of plenty locality and those of little locality are very harmful. However, such kinds of conflicts frequently occur in HPC. On-Chip Memory can avoid such interferes because software can do the control explicitly.

2. suppress of unnecessary data transfer For non-consecutive or stride data access, unnecessary data in the same line is transferred from off-chip memory. This is the waste of valuable off-chip bandwidth and cache space. On-Chip memory avoids this unnecessary data transfer by the block-stride transfer mechanism of page-load and page-store.

3. improvement of effective bandwidth

For consecutive data access, the number of data transfer is reduced by invoking a large amount of data transfer at a time. This is helpful for making effective off-chip bandwidth closer to its theoretical bandwidth. This optimization gets more important when the access latency increases. In ordinary cache, this could be possible by using larger line. However, this also increases the opportunity of line conflicts and unnecessary data transfer. On-Chip Memory realizes a large amount of consecutive data transfer without these sacrifices.

Since off-chip bandwidth will not grow as fast as on-chip bandwidth, reducing off-chip traffic is essentially required. The first and the second benefits contribute to the reduction of off-chip traffic. The third optimization contributes to the relaxation of performance degradation caused by off-chip access latency.

## 3 Optimization of Benchmarks

In this paper, performance of cache-based architecture and SCIMA is evaluated and compared by using two kernels (CG, FT) of NAS Parallel Benchmarks[7] and QCD (Quantum ChromoDynamics) computation[8]. QCD is a practical application used at Center for Computational Physics, University of Tsukuba[9]. In the evaluation, each benchmark is optimized for cache architecture and SCIMA respectively. In this section, we describe the overview of the benchmarks and explain how to optimize them for the two architectures.

Table 2 shows the data sets of target programs used in the evaluation. For saving simulation time, Class-W was selected in CG and FT. On the other hand, the data size of QCD is fairly practical[10]. In QCD, we measured the required time for executing the most time consuming part once. This part is executed so many times in the real computation.

As mentioned later in Section 4.2, we assume the total size of cache/On-Chip is 32KB. This size is quite small but reasonable for evaluating class-W benchmark because cache and On-Chip Memory is usually smaller than the whole data set in HPC.

| program   | data set                                                                              |

|-----------|---------------------------------------------------------------------------------------|

|           | class W                                                                               |

| Kernel CG | - $p: 7000$ elements (double-precision)                                               |

|           | - $p: 7000$ elements (double-precision)<br>- $A: 7000 \times 7000$ (double-precision) |

|           | class W                                                                               |

| Kernel FT | - $128 \times 128 \times 32$ (double-precision complex)                               |

|           | "G,R,B,V,T": total 2.5MB                                                              |

| QCD       | "U": 1.5MB                                                                            |

|           | "M": 3MB                                                                              |

Table 2. Data set of each programs

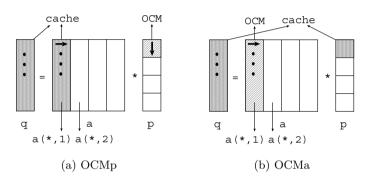

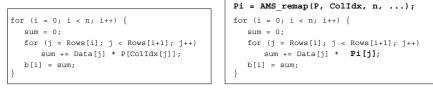

Fig. 4. Optimization for SCIMA in Kernel CG

## 3.1 NPB Kernel CG

The time consuming part of CG forms q = Ap, where A is sparse matrix and p and q are vectors. The structure of the innermost loop is "sum = sum + a(k)\*p(colidx(k))". Therefore, A is accessed consecutively whereas p is accessed in random. Another characteristic is that A has no reusability whereas p has reusability.

The original code is optimized for cache-based architecture and SCIMA in several ways as follows.

**Cache-Opt:** To exploit the reusability of p, blocking optimization is applied. The computation is blocked in the same way as shown in Fig. 4 except that all the data is of course accessed through cache.

In addition to blocking optimization, the program is optimized for SCIMA in the following two ways.

**SCIMA OCMp:** The vectors p is accessed through On-Chip Memory as shown in Figure 4-[a]. This optimization intends to have the benefit 1 of Section 2.6.

Using this optimization, the reusability of vectors p can be fully utilized without interference within elements of the blocked vector p itself or other arrays.

**SCIMA OCMa:** The sparse matrix A is accessed through On-Chip Memory as shown in Figure 4-[b]. This optimization intends to have the benefit 2 of Section 2.6. High effective bandwidth is expected through this optimization because large amount of data is transferred at once. Through this optimization, it is expected that reusability of vectors p is exploited better because no interference between p and A occurs. This is the benefit 1 of Section 2.6.

## 3.2 NPB Kernel FT

The most time consuming part of this kernel is 3-D FFT. The FFT algorithm has stride data access where the stride size is the power of 2. This leads to frequent line conflicts. Moreover, there are plenty of temporal locality in the core FFT part. Therefore, in the original benchmark code, blocking optimization is applied and each tile is copied into a consecutive temporary area. Although the stride data access still occurs in the part of data copy, frequent line conflicts are avoided during the core FFT calculation. Because blocking optimization has already been applied to the original code, we call the original code **Cache-Opt**.

**SCIMA:** In SCIMA, the temporary area for data copy is allocated on On-Chip Memory. The data copy procedure is realized as stride data transfer from Off-Chip Memory into On-Chip Memory. Thus, the benefit 3 of Section 2.6 is expected. Moreover, reusability in the FFT computation would be exploited better because no interference occurs in On-Chip Memory. This is the benefit 1 of Section 2.6.

## 3.3 QCD Computation

QCD is dynamics governed by quantum field theory, which is a problem of particle physics. In this theory, strongly interacting particles called hadrons are made of fundamental quarks and gluon. Numerical simulation of QCD is formulated on 4-dimensional space-time lattice.

In QCD computation, most of the computation is spent in solving a linear equation. The BiCGStab method, which is an iterative algorithm, is used for solving the linear equation. We analyze the performance of the iteration in BiCGStab.

The iteration consists of RBMULT, LOCALMULT and other routines called inter-MULT. Note that RBMULT routine is the most time consuming part. Table 3 illustrates the computation structure of the iteration. Lattice space is divided into even and odd parts. For example, G\_e and G\_o represent even and odd parts of array G respectively. The second line of Table 3, "B\_e(0.5), U(1.5)  $\rightarrow$  G\_o(0.25)", for instance, indicates that 0.25MB of array G\_o is computed by accessing 0.5MB of array B\_e and 1.5MB of array U. Each array has the following characteristics.

- G,R,B,V,T: These arrays have high inter-routine reusability. In addition, they are accessed utmost 8 times in each RBMULT routine.

- U: This array is used only in RBMULT routine which is called 4 times in the iteration. In each RBMULT, U is accessed only once.

- M: This array is accessed only in LOCALMULT routine. Moreover, only even or odd part of M is accessed in one LOCALMULT. Thus, each data of M is accessed only twice in one iteration.

| Routine      | source                | $\rightarrow$ | destination    |

|--------------|-----------------------|---------------|----------------|

| inter-MULT 1 |                       |               |                |

| RBMULT       | $B_e(0.5), U(1.5)$    | $\rightarrow$ | $G_0(0.25)$    |

| LOCALMULT    | $G_0(0.25), M_0(1.5)$ | $\rightarrow$ | $G_0(0.25)$    |

| RBMULT       | $G_0(0.5), U(1.5)$    | $\rightarrow$ | $V_{e}(0.25)$  |

| LOCALMULT    | $V_{0.25}, M_{0.25}$  | $\rightarrow$ | $V_{e}(0.25)$  |

| inter-MULT 2 |                       |               |                |

| RBMULT       | $R_{e}(0.5), U(1.5)$  | $\rightarrow$ | $G_0(0.25)$    |

| LOCALMULT    | $G_0(0.25), M_0(1.5)$ | $\rightarrow$ | $G_0(0.25)$    |

| RBMULT       | G_ $o(0.5), U(1.5)$   | $\rightarrow$ | $T_{e}(0.25)$  |

| LOCALMULT    | $T_e(0.25), M_e(1.5)$ | $\rightarrow$ | $T_{-e}(0.25)$ |

| inter-MULT 3 |                       |               |                |

Table 3. Iteration Structure in QCD (accessed data size [MB])

To summarize these characteristics, while G, R, B, V and T have plenty of reusability, U and M have no intra-routine reusability and a little inter-routine reusability. However, since the iteration is repeated so many times, even U and M are reused over the repeated iterations. We have optimized this computation as follows.

**Cache-Opt:** To exploit reusability of "G,R,B,V,T", blocking optimization is applied.

**SCIMA:** "U,M" are accessed simultaneously with "G,R,B,V,T" in the iteration loop. Therefore, if only cache is provided, the blocks of "G,R,B,V,T", which have plenty of reusability, may be flushed out from the cache because of the interferences with "U,M". To avoid the problem, this code is optimized for SCIMA as follows. "G,R,B,V,T" are still accessed through cache because LRU algorithm would be the best for handling them. On the other hand, "U,M" are accessed through On-Chip Memory to avoid interference with "G,R,B,V,T". Moreover, high throughput can be obtained by large data transfer size because "U,M" are accessed consecutively to some extent. These optimizations intend to have the benefit 1 and benefit 2 of Section 2.6.

| Execution unit                  |                       |

|---------------------------------|-----------------------|

| - integer                       | 2                     |

| - floating-point (multiply-add) | 1                     |

| - floating-point (div,sqrt)     | 1                     |

| - load/store                    | 1                     |

| Cache/On-Chip Memory latency    | 2cycle                |

| Cache(On-Chip Memory) size      | 32KB                  |

| Cache associativity             | 4way                  |

| Cache line size                 | 32, 64, 128, or 256B  |

| page size                       | 4KB                   |

| Instruction cache accesses      | all hit               |

| Branch prediction               | perfect               |

| Data cache structure            | lock-up free L1 cache |

| Execution order                 | out-of-order          |

|                                 |                       |

Table 4. Assumptions in the Evaluation

## 4 Performance Evaluation

#### 4.1 Evaluation Environment

SCIMA is defined as an extension of existing architecture. In the evaluation, MIPS IV is selected as the base architecture.

It would be preferable to develop an optimized compiler which can handle the architectural extensions. In the evaluation, however, users specify which data should be located on On-Chip Memory, when those should be transferred between off-chip and on-chip memory, and which location of On-Chip Memory should be used by directives in source programs. Giving directives is not difficult because data accesses are fairly regular. Blocking optimization is also applied by users.

These informations on the usage of On-Chip Memory are specified in source program and compiled by ordinary MIPS compiler. We have developed a preprocessor which inserts these informations into assembly code after the compilation. We have also developed a clock level simulator which accepts the binary object generated by existing compiler and interprets the informations inserted by the preprocessor.

#### 4.2 Assumptions for the Evaluation

Table 4 shows the assumptions used in the evaluation. These are common throughout the evaluation.

We assume total on-chip memory (cache and On-Chip Memory) capacity is 32KB. We employ 4-way associative 32KB cache and assume four kinds of line sizes, 32B, 64B, 128B, and 256B.

|     | cache size (associativity) | On-Chip Memory size |

|-----|----------------------------|---------------------|

| (a) | 32 KB (4 way)              | 0KB                 |

| (b) | 24 KB (3way)               | 8KB                 |

| (c) | 16 KB (2 way)              | 16KB                |

| (d) | 0 KB (0 way)               | 32KB                |

Table 5. Combination of cache and On-Chip Memory

By using the reconfiguration mechanism of section 2.4, four combinations of cache and On-Chip Memory are possible as shown in Table 5. We use configuration (a) as a cache-based architecture and configuration (b) or (c) as SCIMA architecture. Here, configuration (d) is not considered at all. because no scalar variable can be cached in this configuration, which obviously leads to poor performance. In the evaluation, configuration (c) is selected in CG and FT, whereas configuration (b) is selected in QCD. The decision on the configuration depends on the property of optimizations and the size of data set.

The assumptions of perfect instruction cache and branch prediction are reasonable because time consuming part of HPC applications consists of regular loops.

#### 4.3 Classification of Execution Cycles

The execution time is classified into CPU busy time, latency stall, and throughput stall. Total cycles are obtained under the above assumption. Throughput stall is defined as the cycles which could be saved from total cycles if Off-Chip Memory bandwidth were infinite. Latency stall is defined as the cycles which could be saved further if Off-Chip Memory latency were 0 cycle. The rest is the CPU busy time.

Each time is obtained as follows. First,  $C_{normal}$ ,  $C_{th\infty}$ , and  $C_{perfect}$  are measured by simulation. Here,  $C_{normal}$  indicate the cycles under the assumption of Table 4.  $C_{th\infty}$  indicate the cycles where Off-Chip Memory bandwidth is infinite.  $C_{perfect}$  indicate the cycles where Off-Chip Memory bandwidth is infinite and Off-Chip Memory latency is 0cycle. Then, cycles of each category is calculated as follows.

CPU busy time =  $C_{perfect}$ latency stall =  $C_{th\infty} - C_{perfect}$ throughput stall =  $C_{normal} - C_{th\infty}$

## 5 Evaluation Result

#### 5.1 Result

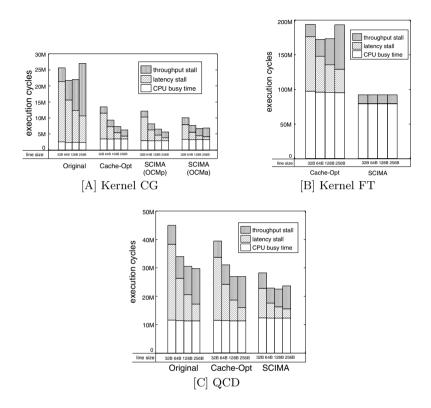

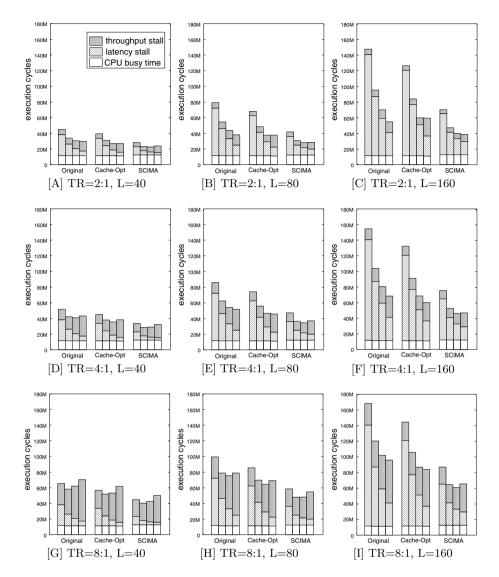

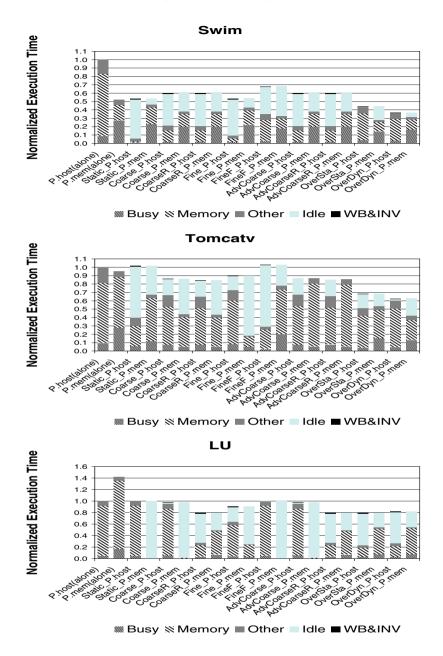

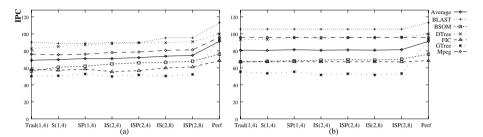

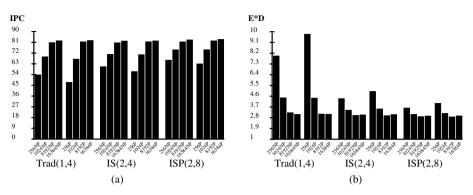

Fig. 5 illustrates the execution cycles and their breakdowns of each program. In this figure, "Original" represents original code which is not modified from the original program. "Cache-Opt" and "SCIMA" represent modified codes optimized for cache and SCIMA architecture respectively. In the case of FT, only "Cache-Opt" and "SCIMA" is given because "Original" code itself have optimizations for cache as mentioned in Section 3.2.

Fig. 5. Evaluation Result

#### Kernel CG

The best partitioning (tiled size) is selected through explorative experiments for each optimization. As a result, "Cache-Opt", "OCMp", and "OCMa" are partitioned into 7, 4, and 7 tiles respectively.

"Cache-Opt" achieves about 1.9 times higher performance than "Original" when the line size is 32B. This is because "Cache-Opt" can exploit the reusability of vector p, and consequently, latency stall and throughput stall are considerably reduced.

"OCMp" in which p is accessed through On-Chip Memory achieves slightly

higher performance than "Cache-Opt". This illustrates the reusability of p is exploited further on On-Chip Memory. This is brought by the benefit 1 of Section 2.6. However, the improvement is not significant. In the Kernel CG, because access pattern of each array except p is regular and consecutive, cache blocking is quite useful.

"OCMa" in which sparse matrix A is accessed through On-Chip Memory is 1.3 times faster than "Cache-Opt" for 32B cache line. This is because line conflicts between p and A are avoided and because large granularity of data transfer by page-load/page-store reduces latency stall. This is the expectant result of optimization strategy in Section 3.1. However, throughput stall of "OCMa" increases for larger cache line because line conflicts between p and *colidx* increase.

"OCMa" achieves the highest performance for 32B and 64B cache line whereas "OCMp" is the fastest for 128B and 256B cache line. This indicates that the best optimization depends on cache line

#### Kernel FT

"SCIMA" achieves 2.1-1.8 times higher performance than "Cache-Opt". This superiority is brought by the effectiveness of block-stride transfer feature of pageload/page-store. Due to this feature, latency stall of "SCIMA" is reduced to less than 1% compared with "Cache-Opt". Throughput stall is also fairly small regardless of cache line size in "SCIMA". On the contrary, throughput stall of "Cache-Opt" increases extremely for larger cache line size because of unnecessary data transfer. As mentioned in Section 3.2, a tile is copied into a temporary area, In the optimization, the size of each tile was selected as 8KB, which is the capacity of one set within data cache, in order to avoid interferences with other data. Then, the blocked data forms a  $4 \times 128$  2-D array (16B for each data). Thus, when cache line is larger than  $64B (= 4 \times 16B)$ , unnecessary data transfers occur. SCIMA does not suffer from this problem due to block-stride data transfer.

#### QCD

To compare "Original" with "Cache-Opt", there is little difference in performance. This illustrates that even if blocking optimization is applied, performance is not improved drastically because of the interferences between "G,R,B,V,T" and "U,M". However, "SCIMA" in which "U,M" are accessed through On-Chip Memory archives 1.4 times higher performance than "Cache-Opt" and 1.6 times higher performance than "Original" for 32B cache line.

Table 6 shows the traffic of Off-Chip Memory for 32B cache line. The second column "cache" represents the traffic between Off-Chip Memory and cache, whereas the third column "On-Chip Memory" represents the traffic between On-Chip and Off-Chip memories. The last column represents the total Off-Chip Memory traffic. As seen from Table 6, the total traffic of "SCIMA" is about 92% compared with "Cache-Opt". This indicates that unwilling interferences are avoided by using On-Chip Memory. In this way, our On-Chip Memory contributes to the reduction of Off-Chip Memory traffic.

| optimization | cache  | che On-Chip Memory |        |

|--------------|--------|--------------------|--------|

| Original     | 26.8MB | 0MB                | 26.8MB |

| Cache-Opt    | 22.4MB | 0MB                | 22.4MB |

| SCIMA        | 10.4MB | 11.4MB             | 20.8MB |

Table 6. Off-Chip Memory Traffic of QCD (32B cache line)

#### 5.2 Discussion

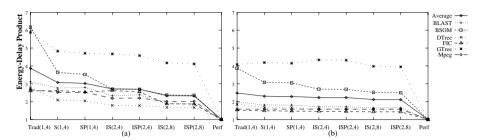

As seen from Fig. 5, for all the benchmarks, latency stall decreases but throughput stall increases for larger line size. This is because more line conflicts are likely to occur for larger line. Therefore, increasing the size of line does not always bring higher performance. Considering the future direction of the semiconductor technology, relative Off-Chip Memory latency is expected to increase and relative Off-Chip Memory bandwidth is expected to decrease. Therefore, it is indispensable to reduce Off-Chip Memory traffic and to make data transfer size larger. Next, we discuss the effectiveness of SCIMA from this viewpoint.

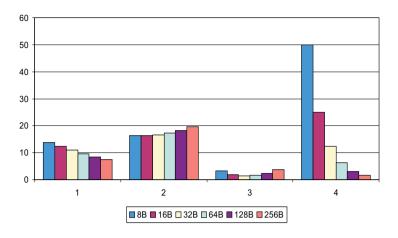

Fig. 6 shows the simulation results of QCD under the assumption representing future semiconductor technology. Performance is evaluated under the three Off-Chip Memory latency (40cycle, 80cycle, 160cycle), and three Off-Chip Memory throughput (4B/cycle, 2B/cycle, 1B/cycle). These assumptions imply future long memory latency and relative narrow bus bandwidth. Fig. 6-[A] is the same as Fig. 5-[C].

From Fig. 6, it is observed that latency stall increases for longer latency and throughput stall increases for narrower bus bandwidth. Consequently, overall performance is greatly degraded as increasing Off-Chip Memory latency and narrowing bus bandwidth. However, the performance of "SCIMA" is less degraded than that of "Cache-Opt". For example, to compare Fig. 6-[A] (4B/cycle Off-Chip Memory throughput and 40cycle Off-Chip Memory latency) with Fig. 6-[I] (1B/cycle Off-Chip Memory throughput and 160cycle Off-Chip Memory latency) for 128B cache line, performance disparity between "Cache-Opt" and "SCIMA" is widened from 1.2 to 1.4. This result indicates that effectiveness of SCIMA will grow in the future.

#### 6 Related Works

There have been many studies on integrating on-chip memory into processor chip besides a cache. Ranganathan et. al.[11] proposed associativity-based partitioning for reconfigurable cache. The mechanism of their cache is similar to our reconfigurable on-chip memory. Chiou et. al.[12] also proposed associativitybased partitioning mechanism which selectively lock some parts of data cache for avoiding unwilling data replacement. However, they do not use their reconfigurable caches as software controllable memory and do not pay much attention

**Fig. 6.** Evaluation Result of QCD under Future Technology ("TR" represents throughput ratio between On-Chip Memory and Off-Chip Memory [On-Chip:Off-Chip] and L represents Off-Chip Memory latency [cycle])

how to supply data from off-chip memory. There is a DSP processor which implements reconfigurable cache[13]. However, it does not focus on the reduction of Off-Chip Memory traffic in HPC. The objective of SCIMA is to make good use of On-Chip Memory by user control and to reduce Off-Chip Memory traffic in HPC.

There have been proposed some processors which adopt small scratch pad RAM [14][15]. However, those scratch pad RAMs are used for specific applications. On the other hand, the target of SCIMA is wide area of HPC applications. Compiler-Controlled Memory[16] is a small on-chip memory which is controlled by compiler. However, this memory is used for only spill code. On-Chip Memory of SCIMA, on the other hand, can be used for all the data if required.

The target of SCIMA is wide area of HPC applications which have large data set. SCIMA realizes flexible and explicit data transfer between on-chip and off-chip memory. This is the main difference between our SCIMA and other works.

### 7 Concluding Remarks

We presented a novel processor architecture *SCIMA* which has software-controllable addressable memory in addition to ordinary cache. The data location and replacement of On-Chip Memory are controlled by software. Due to this feature, SCIMA can control data transfer among memory hierarchy very flexibly. SCIMA has upper compatibility with conventional memory architecture. On-Chip Memory and cache are unified in SCIMA. Therefore, if the whole on-chip memory is used as cache, SCIMA becomes the same as conventional processors.

We presented performance evaluation of SCIMA by using three benchmarks. The evaluation results reveal that SCIMA achieves higher performance than cache-based architecture by reducing both throughput stall and latency stall. The benefit of SCIMA comes from the following features. Firstly, SCIMA can fully exploit temporal locality because unwilling line conflicts are successfully avoided. Secondly, SCIMA can suppress unnecessary data transfer by block-stride data transfer. Finally, SCIMA can improve effective bandwidth by realizing a large amount of consecutive data transfer.

Considering the future direction of the semiconductor technology, off-chip memory latency is expected to increase and relative off-chip memory bandwidth is expected to decrease. Therefore, it is indispensable to reduce off-chip memory traffic and to make data transfer size larger. SCIMA achieves high performance by realizing both issues. This indicates that effectiveness of SCIMA will grow in the future.

From these results, it is concluded that SCIMA is very effective for high performance computing. We are planning to evaluate SCIMA on other wider variety of applications and to design SCIMA in detail for verifying the impact on clock frequency.

## Acknowledgment

We thank the members of the Research Center for Computational Physics, University of Tsukuba for their helpful comments and suggestion. This work is partially supported by the Research for the Future Program of JSPS in the "Computational Science and Engineering" Field (Project No. JSPS-RFTF 97P01102).

### References

- D. Burger, J. Goodman, and A. Kagi, "Memory Bandwidth Limitation of Future Microprocessor", Proc. 23rd Int'l Symp. on Computer Architecture, pp.78–89, 1996

- D. Callahan and A. Porterfield, "Data Cache Performance of Supercomputer Applications", Proc. of Supercomputing '91, pp.564–572, 1990.

- M. Lam, E. Rothberg and M. Wolf, "The cache performance and optimizations of Blocked Algorithms", Proc. ASPLOS-IV, pp.63–74, 1991

- S. Coleman and K. S. McKinley, "Tile size selection using cache organization and data layout", Proc. of PLDI'95, pp.279–289, June 1995.

- P. Panda, H. Nakamura, N. Dutt and A. Nicolau, "Augmenting Loop Tiling with Data Alignment for Improved Cache Performance", IEEE Transactions on Computers, Vol 48, No. 2, pp.142–149, 1999

- M. Kondo, H. Okawara, H. Nakamura, T. Boku and S. Sakai, "SCIMA: A Novel Processor Architecture for High Performance Computing", Proc. of HPC-Asia 2000, pp.355–360, May 2000

- D. Bailey, T. Harris, W. Saphir, R. Wijngaart, A. Woo, and M. Yarrow, "The NAS Parallel Benchmarks 2.0", NASA Ames Research Center Report, NAS-05-020, 1995.

- S. Aoki, R. Burkhalter, K. Kanaya, T. Yoshié, T. Boku, H. Nakamura, Y. Yamashita, "Performance of lattice QCD programs on CP-PACS", Parallel Computing 25, pp.1243–1255, 1999

- 9. http://www.rccp.tsukuba.ac.jp/

- M. Kondo, H. Okawara, H.Nakamura, and T. Boku, "SCIMA: Software Controlled Integrated Memory Architecture for High Performance Computing", ICCD-2000, pp.105–111, Oct. 2000

- P. Ranganathan, S. Adve and N. Jouppi, "Reconfigurable Caches and their Application to Media Processing" Proc. 27th Int'l Symp. on Computer Architecture, pp.214-224, 2000

- D. Chiou, P. Jain, S. Devadas, and L. Rudolph, "Application-Specific Memory Management for Embedded Systems Using Software-Controlled Caches", Technical Report CGS-Memo 427, MIT, 1999

- S. Agarwala, C. Fuoco, T. Anderson, and D. Comisky, "A multi-level memory system architecture for high-performance DSP applications", ICCD-2000, pp.408– 413, Oct. 2000

- Sony's emotionally charged chip. *MICROPROCESSOR REPORT*, Vol. 13, No. 5, 1999.

- 15. Strongarm speed to triple. MICROPROCESSOR REPORT, Vol. 13, No. 6, 1999.

- K. Cooper and T. Harvey, "Compiler-controlled memory", Proc. of ASPLOS-VIII, pp.2–11, 1998.

# **Content-Based Prefetching: Initial Results**

Robert Cooksey, Dennis Colarelli, and Dirk Grunwald

University of Colorado Department of Computer Science Boulder, CO 80309 {rcooksey, dennisc, grunwald}@cs.colorado.edu

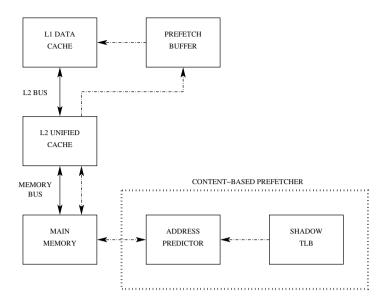

**Abstract.** Memory latency, the time required to retrieve a specified datum from memory, is currently the largest limitation for high-performance computers. Memory prefetching attempts to reduce the memory latency by moving data from memory closer to the processor. Different prefetching mechanisms attempt to model access patterns that may be used by programs. For example, a stride or stream prefetcher assumes that programs will access memory in a linear pattern. In applications that utilize a large number of dynamically allocated objects, the memory access patterns can become very irregular, and difficult to model.

This paper proposes *content-based prefetching*, a method of data prefetching that attempts to overcome the problems introduced by the irregular memory access patterns seen in pointer-intensive applications, thus allowing prefetches of "pointer chasing" references. Content-based prefetching works by examining the content of data as it is moved from memory to the caches. Data values that are likely to be addresses are then translated and pushed to a prefetch buffer. Content-based prefetching has the capability to prefetch sparse data structures, including graphs, lists and trees.

In this paper we examine the issues that are critical to the performance and practicality of content-base prefetching. The potential of the content-aware prediction mechanism is demonstrated and compared to traditional stride prefetching techniques.

# 1 Introduction

#### 1.1 Overview

Most prefetch mechanisms work by recording the history of load instruction usage, indexing on either the address or the effective address of the load instruction [6,20]. This requires the prefetcher to have observed the load instruction one or more times before an effective address can be predicted. This method can work well for loads that follow an arithmetic progression, but does not show good performance for pointer loads that may exhibit a more irregular access pattern. An alternative mechanism is to try to find a correlation between miss addresses and some other activity. The correlation [5] and Markov [10] prefetchers record patterns of miss addresses in an attempt to predict future misses, but this technique requires a large correlation table and a training phase for the prefetcher.